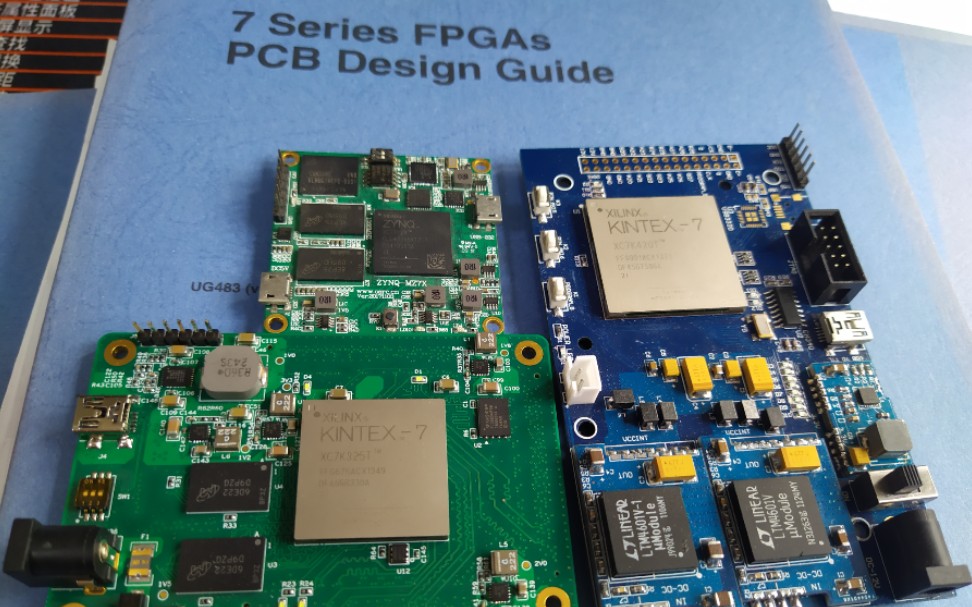

【硬件设计】设计一个FPGA学习板(PART1概述)

NSAIDs_不限量:

NSAIDs_不限量:

bga是用双面板扇出的?还是4层或者6层,多层板打板费用我都不敢看了

【回复】回复 @白嫖_自动化 :K7最小的芯片484pin,也就是22*22的BGA,假设两个pin之间只走一根线,一层只能扇出最边上的两排pin,如图12*12的BGA,逗号pin可扇出,(22的懒得画了,画了12*12的左上角)。

,,,,,,,,,,,,

,,,,,,,,,,,,

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

,,。。。。。。。。。。

如果你有两层走线层那你可以再打孔扇出两排(,和 ;总共四排 ):

,,,,,,,,,,,,

,,,,,,,,,,,,

,,;;;;;;;;;;

,,;;;;;;;;;;

,,;;。。。。。。。。

,,;;。。。。。。。。

,,;;。。。。。。。。

,,;;。。。。。。。。

,,;;。。。。。。。。

,,;;。。。。。。。。

,,;;。。。。。。。。

,,;;。。。。。。。。

V(总共22排减掉四排的正方形)

但是!两层板的话,中间的 (22-4) ^ 2 = 324 个pin理论上都无法扇出,而且BGA的电源和地基本上都是在中间,两层板芯片核电压都连不上,所以的确是不能用的[偷笑]

【回复】回复 @鸢ー折紙み :肯定的啊,你看我那句话的意思还不明白吗[吃瓜]又不是不能用

【回复】回复 @WhosAWhiz :ns级别的精度

要计算高频电路的等效电路与综合影响

飞线是要谨慎的 哆菈A凛:

哆菈A凛:

GTX没有引出来?我基本引脚扇出来用了14层,如果不用GTX的话,10层或者12层SI和PI性能会更好。 薛定谔的猫power:

薛定谔的猫power:

最近在研究以太币算法移植FPGA不知道up有没有兴趣 不稳定海洋:

不稳定海洋:

标题没全部加载出来,看成设计FPGA,吓死我了!😂 捉羊大师:

捉羊大师:

劝你不要用PG控制EN,芯片EN没开启的时候,PG的输出异常。 Red-bress:

Red-bress:

这玩意多少钱一片。。。

说出来让我死心。。。。

【回复】回复 @Red-bress:会逐渐更新

【回复】回复 @Red-bress :哪里可以找到我:

1.微信:Yiludaifei(一路带飞的谐音)2.qq群:664137425(付费群)

【回复】回复@海贼王路飞_一路带飞 :

资料哪里搞?

不如建个群吧